Идея статьи родилась после прочтения многочисленных источников в интернете по барьерам и моделям памяти.Так же, был просмотрены соответствующие видео с разъяснением. Много где в целом всё достаточно хорошо разжевано. Статья не претендует на исчерпывающий материал. Скорее, это обзорное описание на тему модели памяти в связке с RISC-V. Не рассчитана на entry level, рекомендуется сперва почитать что нибудь вводное.

Рубрика «risc-v» - 3

Небольшие заметки про модель памяти на примере RISC-V

2025-03-29 в 9:15, admin, рубрики: risc-v, модель памятиCтандарт RISC-V RV32I и математика с плавающей точкой

2025-03-25 в 11:49, admin, рубрики: gcc, r32l, risc-vНикакое серьезное вычисление невозможно без чисел с плавающей запятой, но, как известно, стандарт RISC-V RV32I не содержит команд умножения и деления. Достаточно ли будет в софт-ядре реализовать стандарт RV32I, чтобы можно было вычислять что-то серьезное? В этой статье на примере RISC-V процессора YRV, описанного в книге Inside an Open-Source Processor, мы рассмотрим, как, используя компилятор GCC, рассчитать такие тригонометрические функции, как синус, косинус, тангенс, выведем на экран результат и даже нарисуем олдскульную синусоиду в VGA-режиме.

Векторизация в RISC-V. Основы

2025-03-21 в 11:00, admin, рубрики: asic, risc-v, simd, SystemVerilog, векторизацияМногие современные вычислительные задачи, в частности повсеместная обработка изображений и звука или работа с матрицами для ИИ, хорошо поддаются параллелизации на уровне данных. Входные данные таких задач представлены в виде большого вектора данных, элементы которого можно обрабатывать независимо. Чтобы ускорить вычисления с векторами, производители процессоров добавили в архитектуры специальные Single Instruction, Multiple Data инструкции, которые позволяют работать за одну инструкцию сразу с несколькими элементами.

Открытая архитектура для мобильных устройств и систем управления технологическим процессом: развитие ПО для RISC-V

2025-03-10 в 13:19, admin, рубрики: open source, risc-v, альянс, митап, открытая архитектураЕсли вы хотите узнать, готов ли RISC-V к мобильным устройствам, как развивается экосистема открытого ПО и какие перспективы ждут технологию в России, то у вас есть планы на пятницу! 14 марта в 19:00 пройдет новый митап российского Альянса RISC-V — независимого объединения разработчиков вычислительной техники и программного обеспечения на основе открытой архитектуры.

Участники события, организованного совместно с YADRO, узнают о новейших тенденциях в экосистеме программного обеспечения для RISC-V, обсудят развитие технологий и смогут задать вопросы экспертам. Читать полностью »

Новинки от производителей ARM- и RISC-V-процессоров последнего времени. Что предлагает рынок?

2025-03-07 в 12:00, admin, рубрики: risc-v, Процессоры, чипыПривет! Сегодня я расскажу о нескольких интересных чипах для серверного сегмента. Процессоры от Intel, недавно представленные корпорацией, описывать не буду: о них и так огромное количество информации. Возьму новые чипы, созданные стараниями менее известных производителей. Если у вас есть что добавить, обязательно пишите в комментариях.

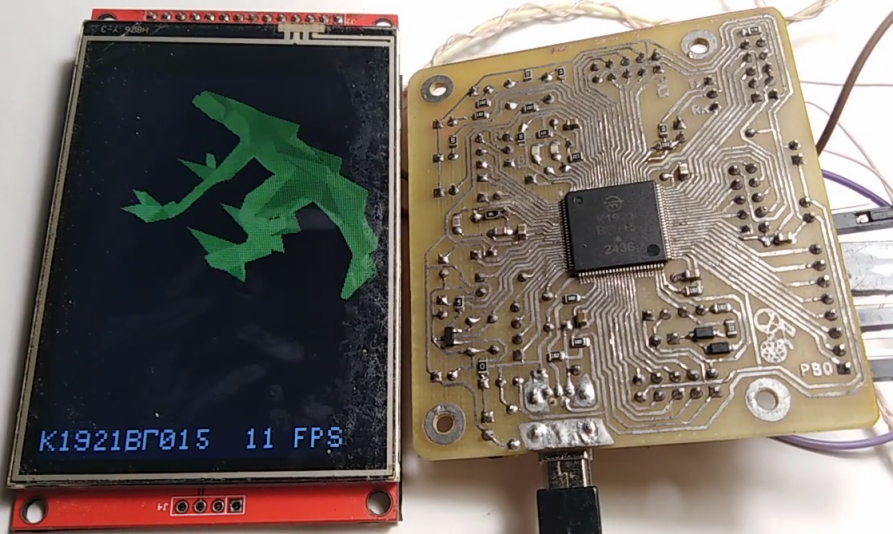

Первые впечатления от 1921вг015, отечественного RISC-V контроллера

2025-02-17 в 11:28, admin, рубрики: 1921вг015, risc-v

Недавно мне в руки противоестественными путями попал интересный представитель RISC-V контроллеров производства НИИЭТ. Упакован он в пластиковый lqfp100 корпус, в котором скрывается ядро на 50 МГц, мегабайт флеш-памяти и 256 кБ оперативки. Разумеется, в наличии и стандартная периферия вроде UART-ов, SPI и USB. А вот из необычного — сигма-дельта АЦП на 16 бит. Ну и всякая неинтересная периферия вроде аппаратных модулей шифрования. Сразу оговорюсь, что тыкаю палочкой я его меньше двух недель, поэтому здесь описаны именно первые впечатления.

Операционная система в 1 000 строках кода (Часть 1)

2025-01-19 в 9:01, admin, рубрики: risc-v, ruvds_перевод, UNIX, ассемблер, операционные системы, Программирование, разработка ос, Си, ядро

Всем привет! В этой небольшой книге (серии статей, — прим. пер.) мы с нуля, шаг за шагом, напишем скромную ОС.

Вы можете насторожиться, услышав, что разработка ОС или ядра, в частности, их базовых функций на удивление проста. Даже система Linux, которая воспринимается как масштабный опенсорсный проект, на стадии версии 0.01 включала всего 8 413 строк кода. Сегодня ядро Linux действительно огромно, но начиналось оно, как и типичный хобби-проект, с крохотной базы кода.

В рамках предстоящей серии статей мы на языке С реализуем базовое переключение контекста, страничное распределение памяти, режим пользователя, командную оболочку, драйвер дискового устройства и операции чтения/записи. И хотя такой объём работы может показаться масштабным, всё это уместится всего в 1 000 строк кода.

Но сразу предупрежу — процесс окажется не так прост, как выглядит на первый взгляд. Самой сложной частью создания собственной ОС является отладка. И мы не сможем использовать для этого printf, пока её не реализуем. Здесь вам потребуется освоить различные техники и приёмы отладки, которые в разработке ПО вы никогда не использовали. В частности, начиная «с нуля», вы будете встречать сложные этапы вроде процесса загрузки и страничной организации памяти. Но не пугайтесь, «отлаживать ОС» мы тоже научимся!

Чем сложнее отладка, тем больше радости от получения рабочего продукта. Так что приглашаю вас погрузиться в захватывающий мир разработки операционных систем!Читать полностью »

Портирование приложения под RISC-V в прямом эфире и не только: 12 лекций по разработке под открытую архитектуру

2025-01-17 в 10:42, admin, рубрики: risc-v, лекции, образование, Процессоры, СофтУже второй год мы проводим бесплатную Зимнюю школу по программированию для RISC-VЧитать полностью »

Рассматриваем циклы процессора в контроллере CH32x035

2025-01-14 в 8:06, admin, рубрики: risc-v, Латентность флэш-памяти, Латентность флэша, микроконтроллер CH32x035, настройка производительности, проблемы от предвыборки, циклы Фон-НейманаКогда мне предстоит начать работу с новым микроконтроллером, я обычно гляжу, а какое у него быстродействие GPIO. Сколько тактов на одну запись уходит по факту. Такая у меня традиция. Было дело, я так выяснил, что китайские клоны STM32 работают с GPIO чуть быстрее, чем оригинал. Для дешёвых контроллеров обычно ничего более интересного такие проверки не выявляют, но традиция есть традиция. Не изменял я ей и при начале освоения CH32x035 на базе RISC-V. И вот для него картинки получились такими интересными, что я решил поделиться ими с общественностью. Не то, чтобы там было что-то революционное, но от привычных мне они точно отличаются.

Разработка на Go, верификация, DevOps и программирование микроконтроллеров на RISC-V: выбирай бесплатный курс

2024-12-13 в 13:39, admin, рубрики: devops, Go, risc-v, верификация, курсыНовость для тех, кто хочет сделать начало следующего года особенным для своего развития. Второй год мы запускаем бесплатные практические курсы по востребованным инженерным направлениям. К уже классическим трекам по верификации, DevOps и Go-разработке добавился новый: «Программирование микроконтроллеров RISC-V: от основ работы с открытой архитектурой до создания собственного устройства». РегистрируйтесьЧитать полностью »