В далеком 2011 году компания Xilinx представила свои первые микросхемы SoC (System On Chip) — Zynq-7000. SoC Zynq сочетает в себе программируемую логику, процессорный модуль и некоторую периферию. Статья не является максимально полным описанием SoC Zynq, а лишь отражает те или иные характеристики, с которыми пришлось столкнуться при разработке устройств на базе SoC Zynq.

Читать полностью »

Рубрика «Процессоры» - 22

Что такое Zynq? Краткий обзор

2020-06-28 в 10:53, admin, рубрики: fpga, zynq, обзор, программирование микроконтроллеров, производительность, Процессоры, создание прошивки, тест скоростиКомпания Ampere анонсировала 128-ядерный ARM-процессор Altra Max

2020-06-25 в 9:59, admin, рубрики: 128 ядер, altra max, Блог компании Selectel, высокая производительность, Компьютерное железо, Процессоры, серверы

Несколько месяцев назад калифорнийская компания Ampere представила первый в отрасли 80-ядерный ARM-процессор Ampere Altra. Этот чип на 64-битной архитектуре предназначен для установки в серверное оборудование, он не для потребительского рынка. Сейчас же компания расширила линейку процессоров, дополнив ее 128-ядерной моделью.

Altra Max совместим с другими моделями Altra и могут устанавливаться в серверы, где уже стоят процессоры компании той же линейки. Вся она базируется на дизайне ARM Neoverse N1, он же лежит в основе процессоров AWS Graviton2 от AWS. Компания Ampere заявила, что новые процессоры позволят повысить производительность оборудования, в чем заинтересованы поставщики облачных услуг.

Читать полностью »

Как x86_x64 адресует память

2020-06-22 в 13:05, admin, рубрики: miran, x86_x64, адресация памяти, Алгоритмы, Блог компании Дата-центр «Миран», Компьютерное железо, память, Программирование, ПроцессорыСегодня я собираюсь поговорить про адресацию памяти: один, казалось бы, небольшой, и тем не менее удивительно непростой элемент семантики команд архитектуры х86_64. В особенности хочется поговорить про команду mov и то, как через только одну эту команду х86_64 пользователю становятся доступны различные методы адресации памяти.

Я не буду говорить про остальные затрагивающие память команды (то есть, благодаря CISC, почти все остальные), команды которые пишут массивные фрагменты памяти (это о тебе, fxsave), или иные касающиеся темы вопросы (модели кода, независящий от адреса код, и бинарная релокация). Я также не буду затрагивать исторические режимы адресации или режимы, которые активны при работе процессора x86_64 не в 64-битном режиме (т.е. любые отличные от long mode с 64-битным кодом).

Некоторые ограничения

Несмотря на кошмарное наследие кодирования команд х86_64, а может и благодаря ему, у адресации памяти есть некоторые ограничения.

Начнем с хорошего:

- На достаточно высоком уровне в архитектуре х86_64 есть всего два режима адресации.

- Все регистры в обоих режимах адресации должны быть строго одинакового размера. Другими словами, мы не можем странным образом смешивать 64, 32 и 16-битные регистры и получать актуальный адрес — в кодировании х86_64 для подобного маневра попросту нет места.

Сколько инструкций процессора использует компилятор?

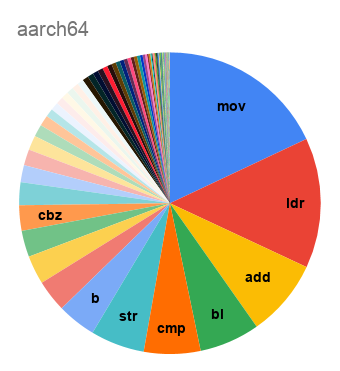

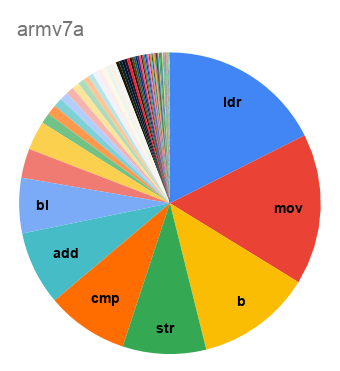

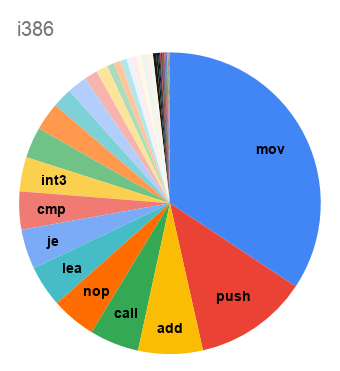

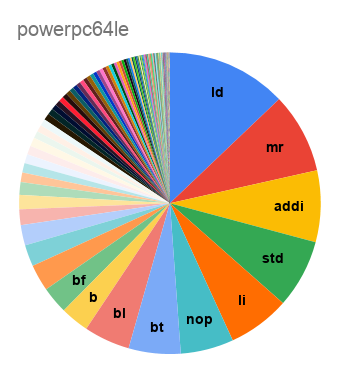

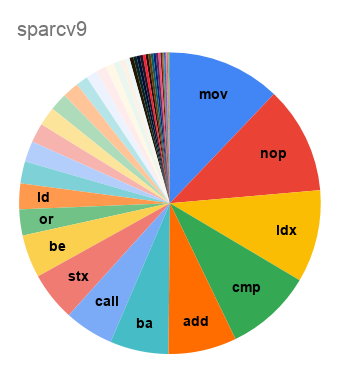

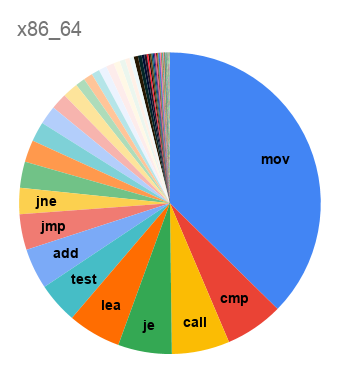

2020-06-16 в 17:04, admin, рубрики: AArch64, ARMv7, i386, powerpc, sparc, x86_64, визуализация данных, Компиляторы, Процессоры, Статистика в ITМесяц назад я попытался сосчитать, сколько разных инструкций поддерживается современными процессорами, и насчитал 945 в Ice Lake. Комментаторы затронули интересный вопрос: какая часть всего этого разнообразия реально используется компиляторами? Например, некто Pepijn de Vos в 2016 подсчитал, сколько разных инструкций задействовано в бинарниках у него в /usr/bin, и насчитал 411 — т.е. примерно треть всех инструкций x86_64, существовавших на тот момент, не использовались ни в одной из стандартных программ в его ОС. Другая любопытная его находка — что код для x86_64 на треть состоит из инструкций mov. (В общем-то известно, что одних инструкций mov достаточно, чтобы написать любую программу.)

Я решил развить исследование de Vos, взяв в качестве «эталонного кода» компилятор LLVM/Clang. У него сразу несколько преимуществ перед содержимым /usr/bin неназванной версии неназванной ОС:

- С ним удобно работать: это один огромный бинарник, по размеру сопоставимый со всем содержимым /usr/bin среднестатистического линукса;

- Он позволяет сравнить разные ISA: на releases.llvm.org/download.html доступны официальные бинарники для x86, ARM, SPARC, MIPS и PowerPC;

- Он позволяет отследить исторические тренды: официальные бинарники доступны для всех релизов начиная с 2003;

- Наконец, в исследовании компиляторов логично использовать компилятор и в качестве подопытного объекта :-)

Начну со статистики по мартовскому релизу LLVM 10.0:

| ISA | Размер бинарника | Размер секции .text | Общее число инструкций | Число разных инструкций |

|---|---|---|---|---|

| AArch64 | 97 МБ | 74 МБ | 13,814,975 | 195 |

| ARMv7A | 101 МБ | 80 МБ | 15,621,010 | 308 |

| i386 | 106 МБ | 88 МБ | 20,138,657 | 122 |

| PowerPC64LE | 108 МБ | 89 МБ | 17,208,502 | 288 |

| SPARCv9 | 129 МБ | 105 МБ | 19,993,362 | 122 |

| x86_64 | 107 МБ | 87 МБ | 15,281,299 | 203 |

В прошлом топике комментаторы упомянули, что самый компактный код у них получается для SPARC. Здесь же видим, что бинарник для AArch64 оказывается на треть меньше что по размеру, что по общему числу инструкций.

А вот распределение по числу инструкций:

Читать полностью »

Читать полностью »

Анатомия RAM

2020-06-15 в 8:01, admin, рубрики: DDR, dram, gddr, ram, Видеокарты, Компьютерное железо, Научно-популярное, ОЗУ, оперативная память, Процессоры

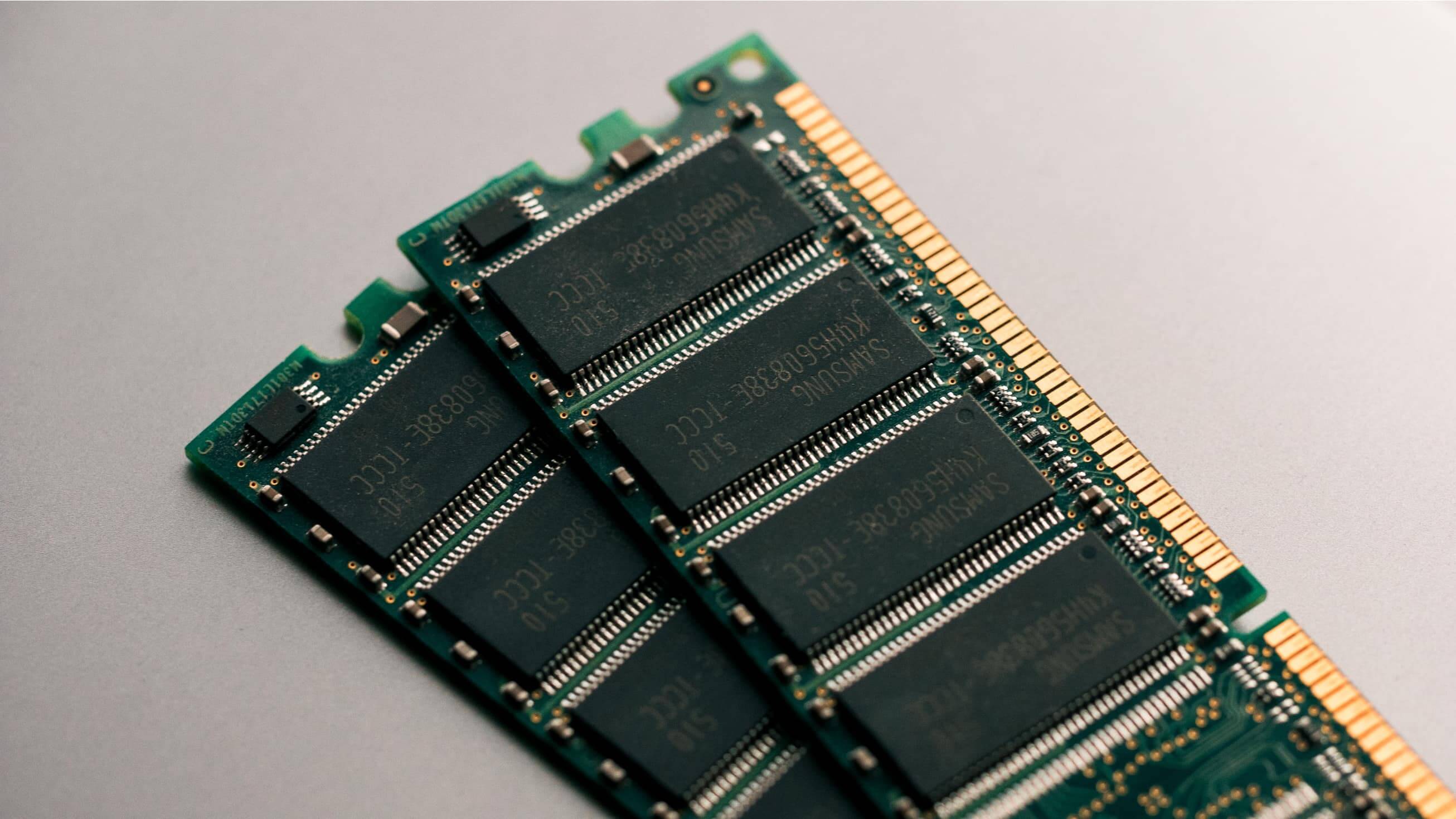

У каждого компьютера есть ОЗУ, встроенное в процессор или находящееся на отдельной подключенной к системе плате — вычислительные устройства просто не смогли бы работать без оперативной памяти. ОЗУ — потрясающий образец прецизионного проектирования, однако несмотря на тонкость процессов изготовления, память ежегодно производится в огромных объёмах. В ней миллиарды транзисторов, но она потребляет только считанные ватты мощности. Учитывая большую важность памяти, стоит написать толковый анализ её анатомии.

Итак, давайте приготовимся к вскрытию, выкатим носилки и отправимся в анатомический театр. Настало время изучить все подробности каждой ячейки, из которых состоит современная память, и узнать, как она работает.

Где же ты, RAM-ео?

Процессорам требуется очень быстро получать доступ к данным и командам, чтобы программы выполнялись мгновенно. Кроме того, им нужно, чтобы при произвольных или неожиданных запросах не очень страдала скорость. Именно поэтому для компьютера так важно ОЗУ (RAM, сокращение от random-access memory — память с произвольным доступом).

Существует два основных типа RAM: статическая и динамическая, или сокращённо SRAM и DRAM.

Мы будем рассматривать только DRAM, потому что SRAM используется только внутри процессоров, таких как CPU или GPU. Так где же находится DRAM в наших компьютерах и как она работает?

Читать полностью »

Реверс-инжиниринг микросхем по фото

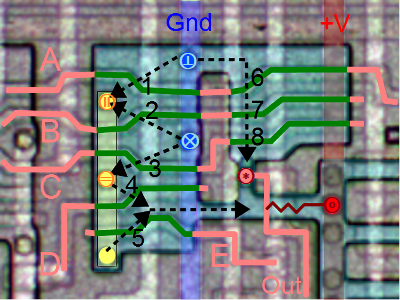

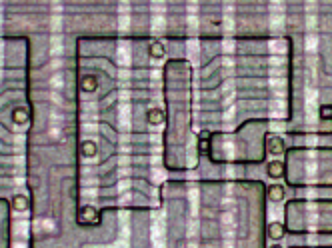

2020-06-08 в 21:57, admin, рубрики: Z80, обработка изображений, Процессоры, реверс-инжиниринг, старое железо, схемотехника, т34вм1Тем, кто любит гикпорн-фотографии от BarsMonster и его товарищей по цеху, наверняка интересно научиться расшифровывать логическую схему по её фотографии. Например, что делает вот этот кусочек Z80?

Яркие вертикальные полосы — это металлические проводники; горизонтальные полосы, от которых видны только тёмные границы — это проводники из поликремния; область неправильной формы с ярко-чёрной границей — это легированная часть кремниевой подложки; желтоватые круги — это соединения между слоями микросхемы.

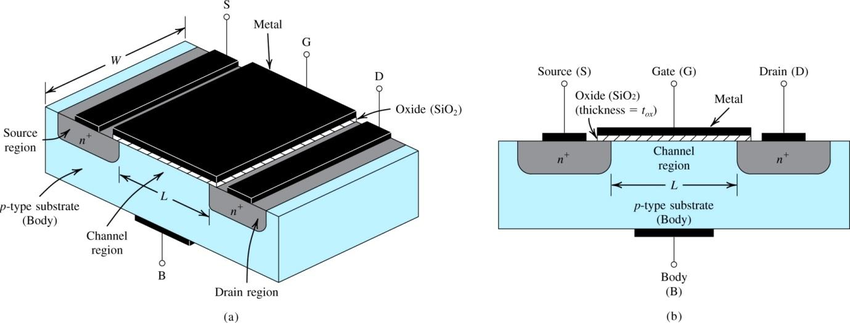

Каждый транзистор образован поликремниевым проводником, пересекающим область легированного кремния:

По традиции, такие транзисторы называют MOSFET («металл-оксид-полупроводник»), даже когда затвор не металлический, а поликремниевый. Автор вполушутку предположил, что ни один производитель поликремниевых транзисторов не хотел называть их POS.

Работа транзистора заключается в том, что когда к затвору приложено положительное напряжение, то легированная область, включающая исток и сток, становится проводящей; когда напряжение с затвора снято, то исток и сток размыкаются.

Вот та же самая фотография с размеченными транзисторами и проводниками: (я добавил в авторскую иллюстрацию обозначения соединений между слоями)

ISA ошибок не прощает

2020-05-21 в 15:14, admin, рубрики: amd, intel, x86, Блог компании Huawei, высокая производительность, Процессоры–X86 – это исторически сложившееся недоразумение,– мэтр и в 80 не утратил полемического задора.

– Вообще-то ей принадлежит 95% серверного рынка, – вяло откликнулся я. Мне не хотелось вступать в спор на сто раз заезженную тему

– А я уже запутался в этих префиксах, — не унимался академик. – 15 байт на инструкцию, это немыслимо!

– Ну, не ice, конечно. Но у кого лучше-то?

– Да у кого угодно, хотя бы у ARM-a.

– Я все же не понимаю. Cложения с умножениями должны быть?

– Должны.

– И сдвиги c логическими операциями?

– Да.

– И загрузки с сохранениями тоже. Какая разница как они называются и кодируются?

Читать полностью »

Intel обнуляет номера моделей процессоров. Но это не точно — будет голосование

2020-04-01 в 6:56, admin, рубрики: Блог компании Intel, Компьютерное железо, обнуление, Процессоры Первые процессоры с маркировкой Core i3/i5/i7 и числовым индексом были выпущены Intel в 2008 году; сейчас, как мы знаем, имеют место десятое поколение Intel Core и модели с числом 10 вначале. При всей логичности такой нумерации в ней имеется скрытый подвох: с ростом индекса он все больше смешивается с другими числами, чего-то обозначающими, и перестает восприниматься как атрибут процессора. Скажем, модель Core 9400 для нас привычна, Core 12800 уже похожа на аккумулятор, а 21280 — вообще что-то из области ВАЗовской классики. Чтобы индексы оставались в психологически комфортном для потребителя диапазоне, Intel рассматривает вариант каждые 10 поколений обнулять первый разряд.

Первые процессоры с маркировкой Core i3/i5/i7 и числовым индексом были выпущены Intel в 2008 году; сейчас, как мы знаем, имеют место десятое поколение Intel Core и модели с числом 10 вначале. При всей логичности такой нумерации в ней имеется скрытый подвох: с ростом индекса он все больше смешивается с другими числами, чего-то обозначающими, и перестает восприниматься как атрибут процессора. Скажем, модель Core 9400 для нас привычна, Core 12800 уже похожа на аккумулятор, а 21280 — вообще что-то из области ВАЗовской классики. Чтобы индексы оставались в психологически комфортном для потребителя диапазоне, Intel рассматривает вариант каждые 10 поколений обнулять первый разряд.

Читать полностью »

Предисловие

Это вторая часть попытки создания TTA процессора в программе Logisim. В процессе создания появилась нужда в дополнительной памяти, в которой могли бы храниться некоторые промежуточные значения, а для этой памяти появилась нужда в изменении управляющего устройства.Читать полностью »

Назад к истокам: рулим компьютером прямо из MBR

2020-03-26 в 21:00, admin, рубрики: mbr, ассемблер, загрузка, КодоБред, ненормальное программирование, низкоуровневое программирование, опкоды, Процессоры, системное программированиеРазворачивал в очередной раз Linux-образ на USB-drive (почему-то им оказался Manjaro, но это совсем другая история), и в голову пробрались странные мысли: BIOS увидел флешку, а дальше-то что? Ну да, там MBR, скорее всего GRUB и… А раз в MBR затесался чей-то кастомный код, значит и простой человек из Адыгеи может запрограммировать что-нибудь на «большом» компьютере, но вне операционной системы.

А так как делать такие штуки на языках высокого уровня слишком жирно, а ассемблеров мы не знаем, будем шпарить прямо на опкодах для 8086.