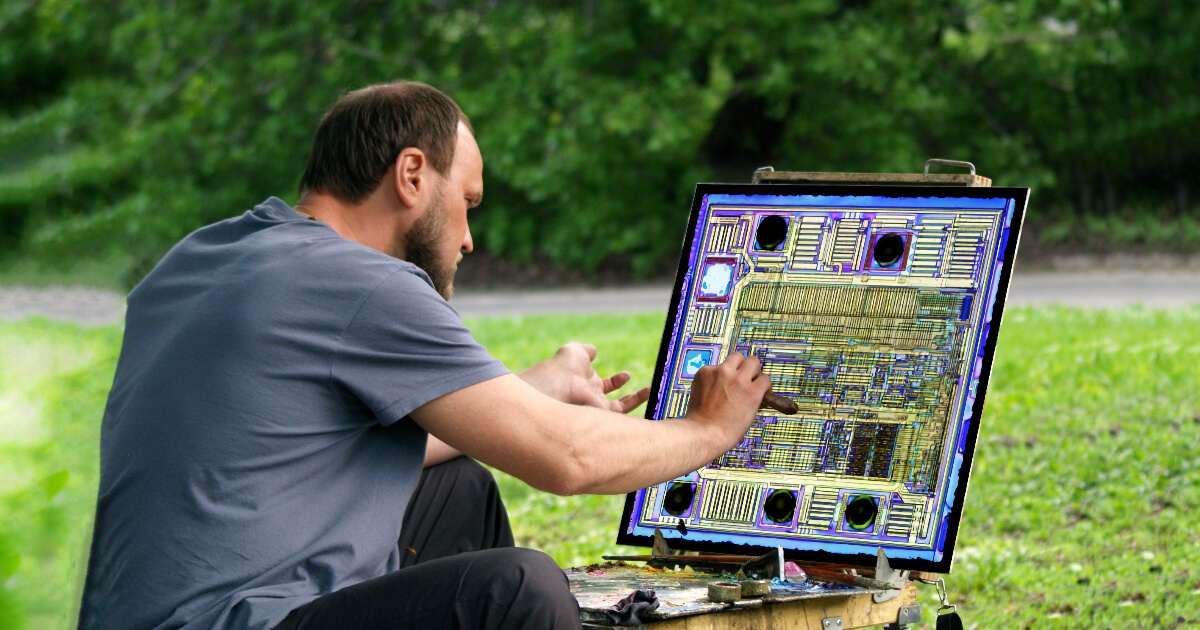

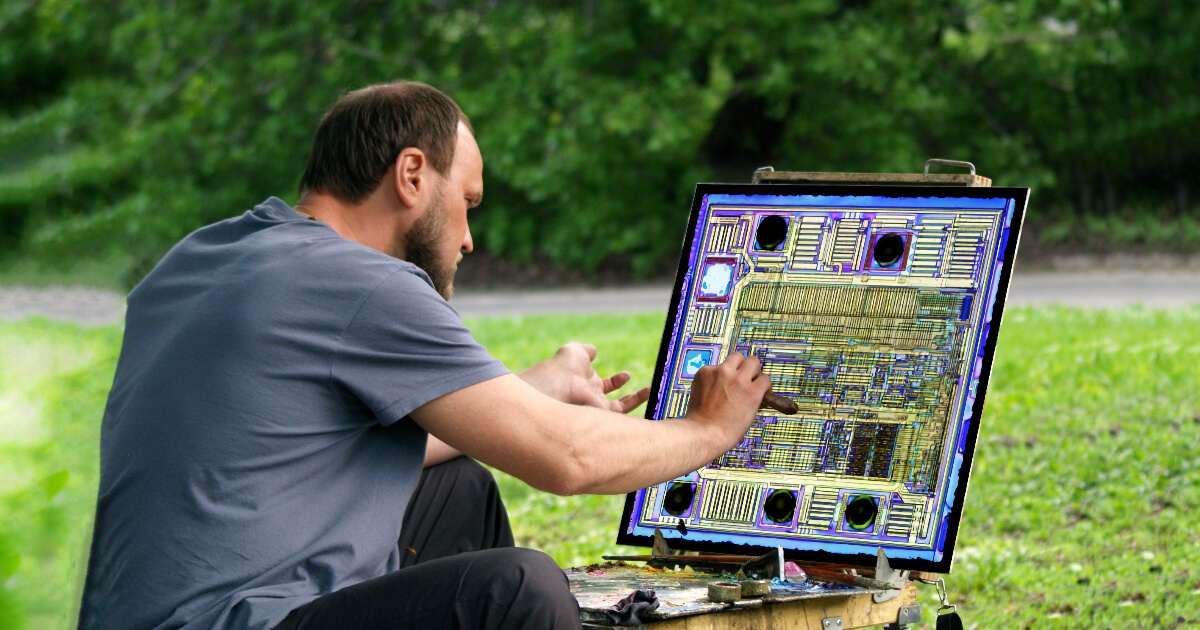

Привет, я Александр Калёнов, аспирант и инженер кафедры интегральной электроники и микросистем в МИЭТ, работаю дизайнером СБИС в «НИИМА «Прогресс». Для хакатона YADRO SoC Design Challenge я создавал задание по топологии, которое мы тут и рассмотрим.

Привет, я Александр Калёнов, аспирант и инженер кафедры интегральной электроники и микросистем в МИЭТ, работаю дизайнером СБИС в «НИИМА «Прогресс». Для хакатона YADRO SoC Design Challenge я создавал задание по топологии, которое мы тут и рассмотрим.

Здравствуйте друзья. Сегодня хотел бы вам рассказать про один интересный сервис, идею создания которого мы в FPGA комунити вынашивали несколько лет и называется он "Сервис аренды отладок". Сразу скажу, что аренда отладок будет бесплатной.

Зачем мы сделали этот сервис? поскольку у нас за время существования FPGA комьюнити Читать полностью »

Газета "Коммерсантъ" опубликовала важный материал "Британия морозит «Байкал». Российские процессоры лишаются доступа к технологиям". К сожалению, авторы заметки никогда не видели то, о чем они написали, то бишь semiconductor IP, и не понимают его природы. Зато его видел я. Поэтому я решил написать к их заметке своего рода толкование:

Что именно британские компании ARM и Imagination продают российским лицензиатам, таким как Байкал? (Спойлер: не патенты, хотя патенты в картину входят)

Чем Apple отличается от Байкала в лицензировании semiconductor IP?

Проектированием простого процессора сейчас никого не удивишь. Любой способный студент может за пару недель написать на верилоге однотактный RISC-V или ARM процессор и синтезировать его для ПЛИС. Процессор будет работать на учебной плате и выполнять простые программы на Си и ассемблере.

Сегодня, в субботу 26 февраля, на Сколковской Школе Синтеза Цифровых Схем Михаил Коробков проводит занятие по технологиям функциональной верификации: constrain solvers, cover bins и concurrent assertions. Примеры, которые мы подготовили для школы, вращаются вокруг протокола AXI для систем на кристалле, вопросы про который спрашивают например на интервью в хардверное отделение компании Meta и другие.

МНОГАБУКАВ.

Всем привет! Расскажу про нашу разработку, которая изменит подход к обработке данных.

Мы разработали новый математический алгоритм обработки данных и программный продукт на его базе (кодек), позволяющий работать со сжатием битовых потоков любого формата (статические/динамические) – то есть, кодек позволяет проводить более глубокое сжатие уже существующих файлов (видео, изображения, архивы и т.д.), так и осуществлять сжатие исходных «сырых» данных.

Прошло всё отлично, 35 человек собралось, 7 докладов выслушано, 12 человек осталось на афтерпати.

Следующее мероприятие пройдет в Москве, Минске, Томске и Санкт-Петербурге в апреле-мае, подробности тут.

Все материалы собраны в отдельные плейлисты - встреча в Москве // слёт в Санкт-Петербурге, под каждым из видео ссылка на презентацию докладчика.

Я долго придумывал вступление к теме FPGAЧитать полностью »